Overview

Clock and timing performance plays a critical role in modern RF, analog, and mixed-signal systems, impacting everything from PLL synthesizers to high-speed data converters and clock distribution networks. Accurately measuring phase noise, jitter, and long-term stability is essential for validating oscillator performance and system timing integrity, crucial for RF, mixed-signal, and test engineers during design validation and bring-up of precision-timing sensitive hardware.

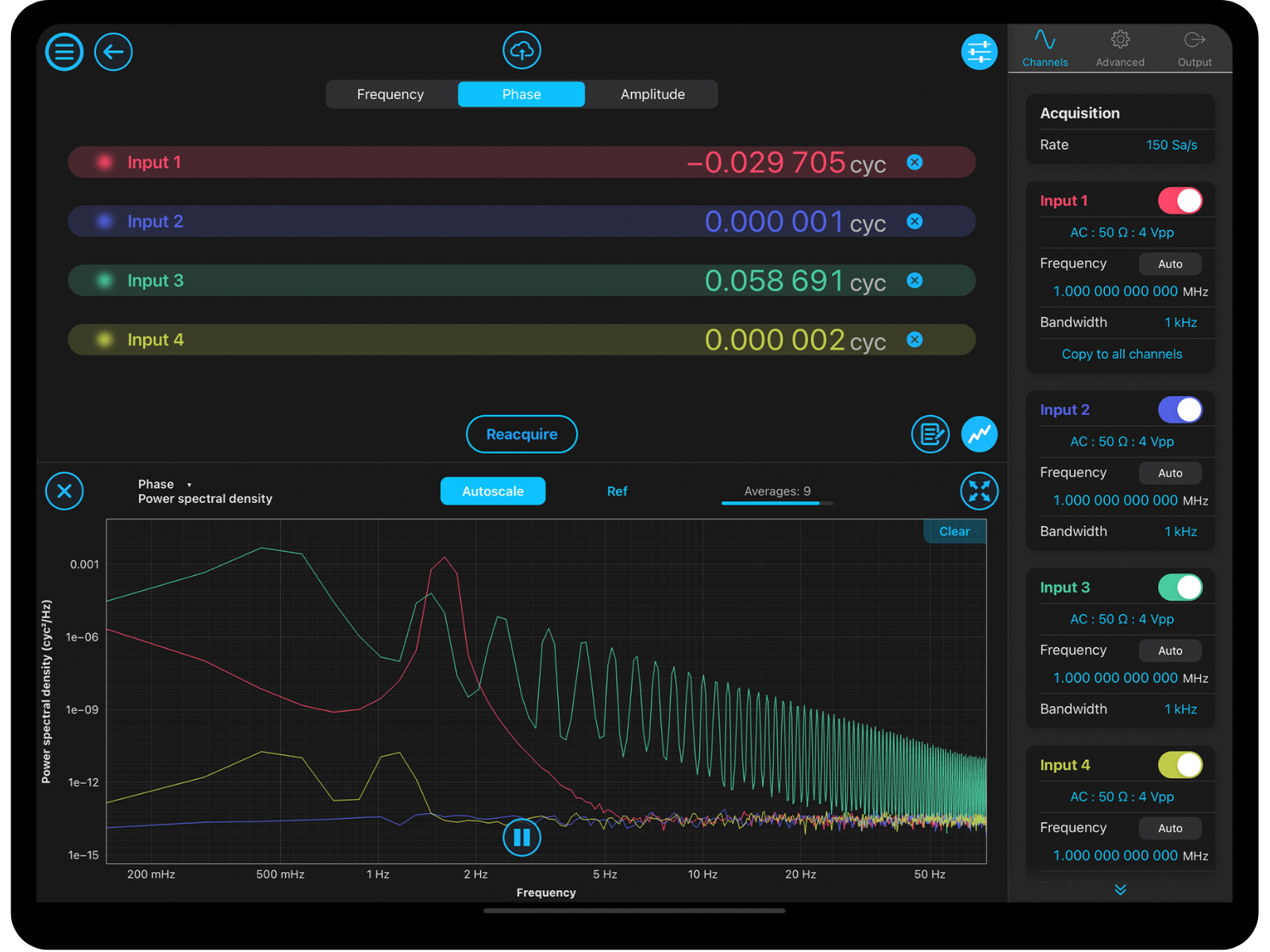

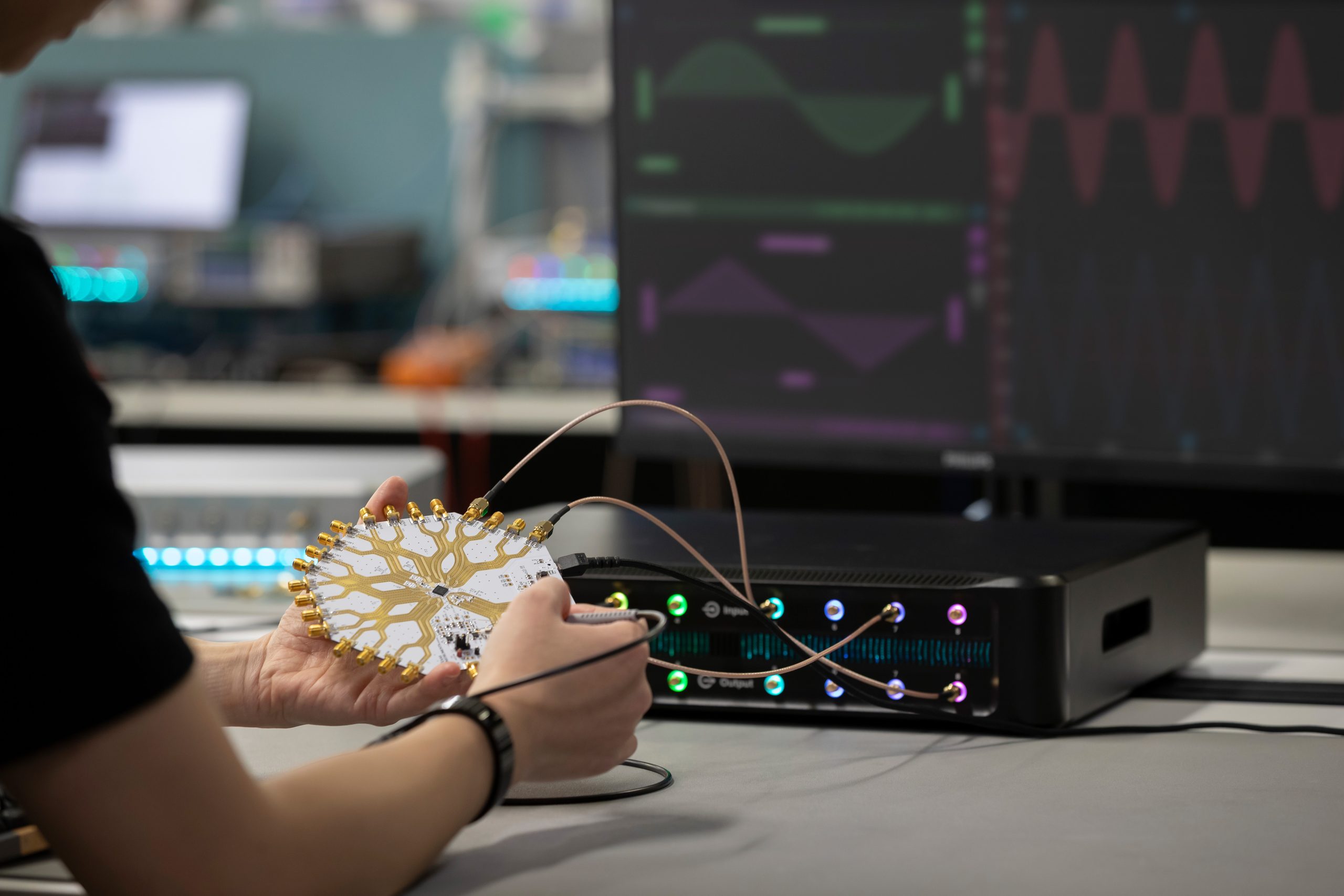

In this webinar, we explore practical techniques for characterizing oscillators, clocks, and timing systems using reconfigurable FPGA-based instrumentation. A live demonstration shows how phase noise evolves during PLL lock acquisition in a voltage-controlled oscillator (VCO) using the Moku:Delta platform.

We also examine precision timing architectures, including GPS-disciplined references and clock blending techniques, which enable designers to generate highly stable timing references while simplifying traditionally complex measurement setups. .

Attendees will learn:

- How phase noise and jitter affect RF and mixed-signal system performance

- Practical techniques for measuring oscillator, clock, and timing system behavior

- How PLL dynamics (including lock acquisition) influence timing stability

- Methods for generating and debugging modern clock distribution systems

Date: April 28, 2026

Speaker: Laura Becerra Ph. D.

Application Engineer,

Liquid Instruments