Proper hardware validation and stress tests before mass production can save millions of dollars on recalls and redesigns. In this application note, the Moku:Go Logic Analyzer/Pattern Generator will be utilized to validate a digital 4-bit adder by toggling inputs and recording the corresponding outputs. Furthermore, the clock rate will be varied to stress test the hardware with increasing clock frequencies giving the user insight into failures.

Moku:Go

Moku:Go combines 15+ lab instruments in one high-performance device, with 2 analog inputs, 2 analog outputs, 16 digital I/O pins and optional integrated power supplies.

Moku:Go combines 15+ lab instruments in one high-performance device, with 2 analog inputs, 2 analog outputs, 16 digital I/O pins and optional integrated power supplies.

Introduction

At the heart of every digital circuit, you will find transistors – fundamental semiconductor devices used to switch electric signals on or off. Various arrangements of these switches give way to logical operators that comprise the fundamental elements of computing. Even the most complicated integrated chips (ICs) can be constructed with these fundamental building blocks. In this application note, we will experience the digital circuit design process by constructing a 4-bit adder circuit with various logic gates. We will utilize the Moku:Go Logic Analyzer/Pattern Generator to validate our design. Later, we will utilize Moku:Go MATLAB APIs to scale up and automate the validation process and run a stress test to determine the maximum clock rate of our circuit.

Circuit Design

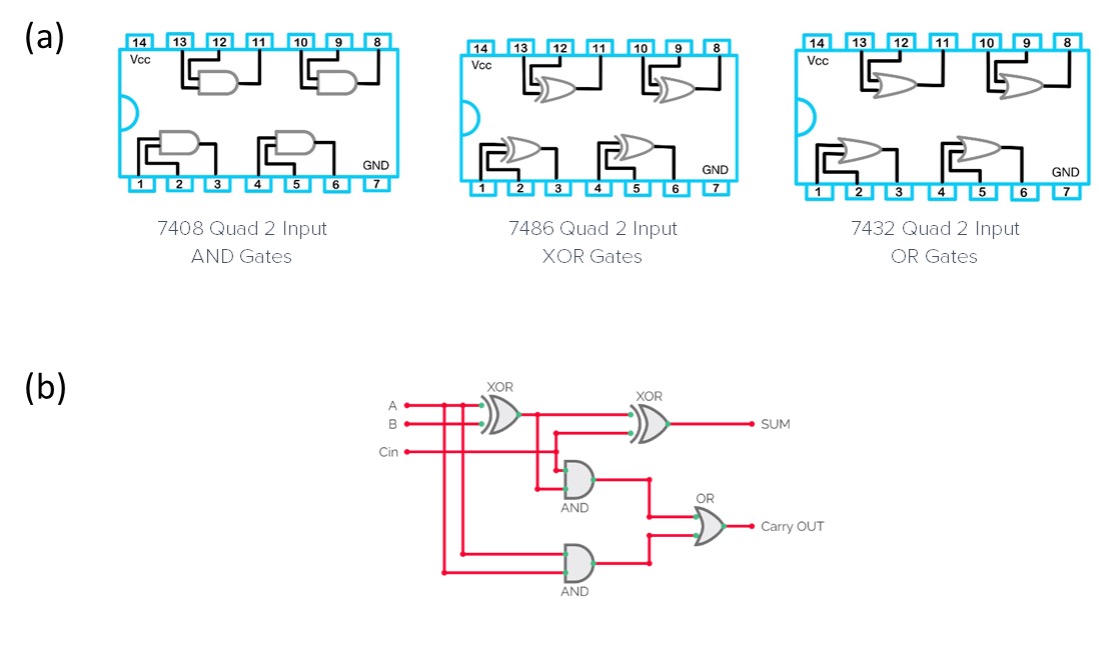

The 4-bit adder was constructed with four full 1-bit adder circuits. Each adder contains two data inputs An and Bn, and one carries input Cin. After the logic operations, it produces the sum of its input Sn, and carries output Cout . For the logic gates, three off-the-shelf logic integrated circuits (ICs) 74LS86, 74LS08, and 74LS32 were used for XOR, AND, OR gates. The detailed layout for the logic ICs and wire connection between logic gates can be found in Figures 1 (a) and (b), respectively.

Figure 1: (a) The logic ICs that were used as AND, XOR, and OR gates. (b) Logic to build a 1-bit full adder.

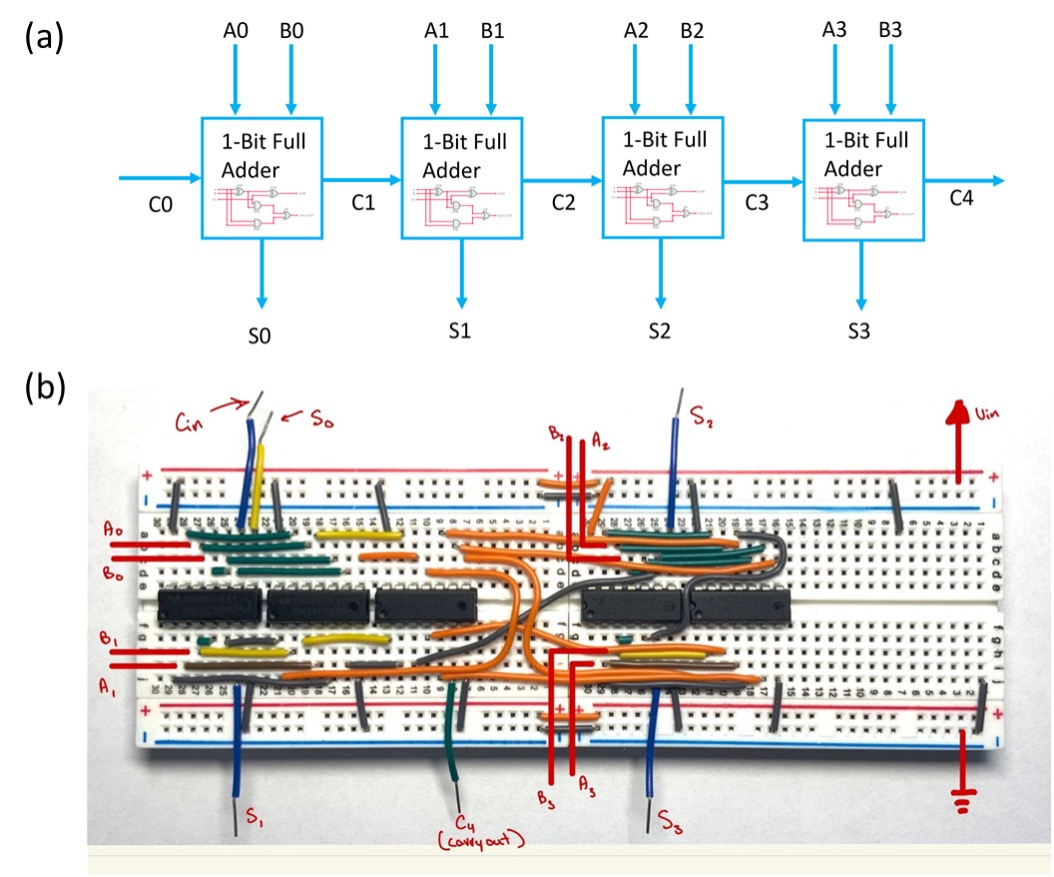

The 4-bit adder circuit was built by connecting the Cout port from the less significant digit adder to the Cin of the next significant digit. Cin for the least significant digit was left as constant low. Cout for the most significant adder (C3) was used to represent the most significant digit for the entire system. The 4-bit adder took two 4-bit numbers via ports A0-3, B0-3, and provided the result on pin S0-3. When both of the inputs were set to 0b1111, C3 would be high. Otherwise, it remained in the low state. Figure 2 shows the schematic (a), and the actual circuit that was built on a breadboard.

Figure 2: (a) The schematic and (b) breadboard layout of the 4-bit adder.

System Validation with Moku:Go’s Logic Analyzer

Instrument Connection

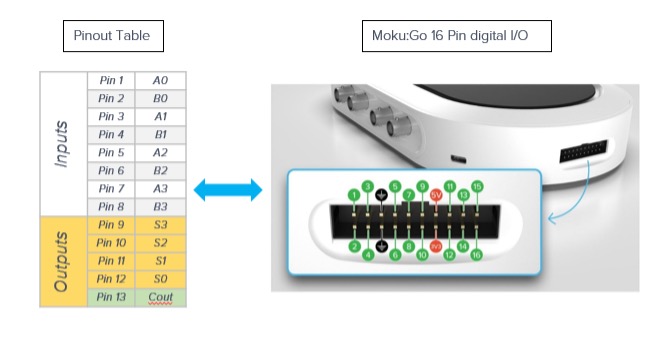

In order to validate the circuit, the inputs and outputs of the 4-bit adders were connected to the Moku:Go 16-pin digital I/O. The detailed connection and pinout map are shown in Figure 3.

Figure 3: The detailed connection map between Moku:Go digital I/O and the 4-bit adder.

Single Input Test

First, the circuit was tested by manually toggling the input levels. In Figure 4, the output (pins 0 to 8) of the Logic Analyzer was set to 0b0101 (A) and 0b0110(b), which translated to 5 + 4 in decimal. From pins 9-12, we read 0b1001, which corresponded to 9 in decimal. The carry out signal on pin 10 was low, which indicated there was no overflow.

Figure 4: The circuit was first tested by manually toggling the input logic levels.

Random Pattern and Stress Test

To scale up the test set and figure out the limit, we utilized the random pattern generation function in the Moku:Go Logic Analyzer. Random patterns with a length of 1024 were generated at variable clock frequencies from 62.5 Hz to 62.5 MHz. Both the randomly generated output patterns and input patterns were recorded and analyzed with MATLAB.

Figure 5: Randomly generated patterns were used to stress test the circuit.

MATLAB Script for Automated Validation

In the automated validation script, the behavior of the logic gates within each adder was explicitly simulated with MATLAB built-in logic operators. The following code snippet read the randomly generated signal on PINs 1 and 2 and calculated the expected output for S0 and C1 for the Full Adder 1 (FA1).

%%%FA1 for i = 1:n S0(i) = xor(xor(data(i,2),data(i,3)),Cin); C1(i) = or(and(Cin,xor(data(i,2),data(i,3))),and(data(i,2),data(i,3))); end

The calculated C1 was then used in the next code block to simulate the behavior of the next FA.

%%%FA2 for i = 1:n S1(i) = xor(xor(data(i,4),data(i,5)),C1(i)); C2(i) = or(and(C1(i),xor(data(i,4),data(i,5))),and(data(i,4),data(i,5))); end

The final hit rate of the entire circuit was calculated via the following block of code:

hit = 0; for i = 1:n if data(i,10)==S3(i) && data(i,11)==S2(i) && data(i,12)==S1(i) && data(i,13)==S0(i) hit = hit +1; end end hit_rate = hit/n*100;

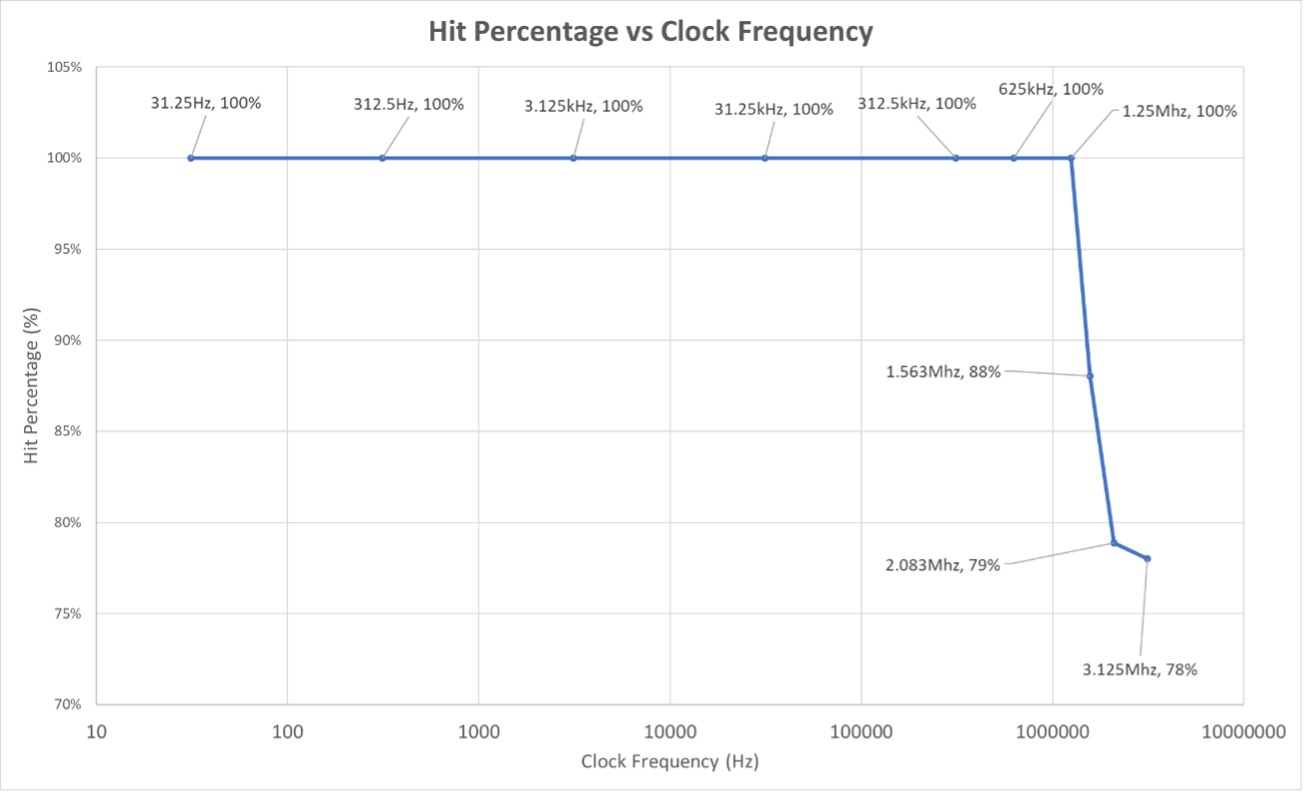

The final hit rate of the 4-bit adder circuit as a function of clock frequencies was plotted in Figure 6. The hit rate was represented as the (Hit Percentage %) on the y-axis and the clock frequency measured in Hertz (Hz) was displayed on the x-axis. The circuit was stable up to 1.25 Mhz. A significant drop-off in performance was observed as the clock rate increased further. We could conclude that the circuit operated under stable conditions between frequencies of 31.25 Hz – 1.25 MHz.

Figure 6: The hit rate of the 4-bit adder as a function of clock frequency.

Conclusion

In this second part of the tutorial, we covered how to utilize MathWorks’ Simulink and HDL Coder to build, validate, and deploy a DSP model on Moku:Pro. Compared to MATLAB only approach, Simulink provides the option to design the DSP via its DSP library and build the model with the fixed-point model from the ground up. It is recommended for building complicated DSP systems.

Have questions or want a printable version?

Please contact us at support@liquidinstruments.com