Overview

During this special presentation, Liquid Instruments Director of Product Ben Nizette shares helpful tips and tricks to turbocharge your test flow with Moku Cloud Compile and ChatGPT, the advanced AI language model sweeping the globe.

Join us to:

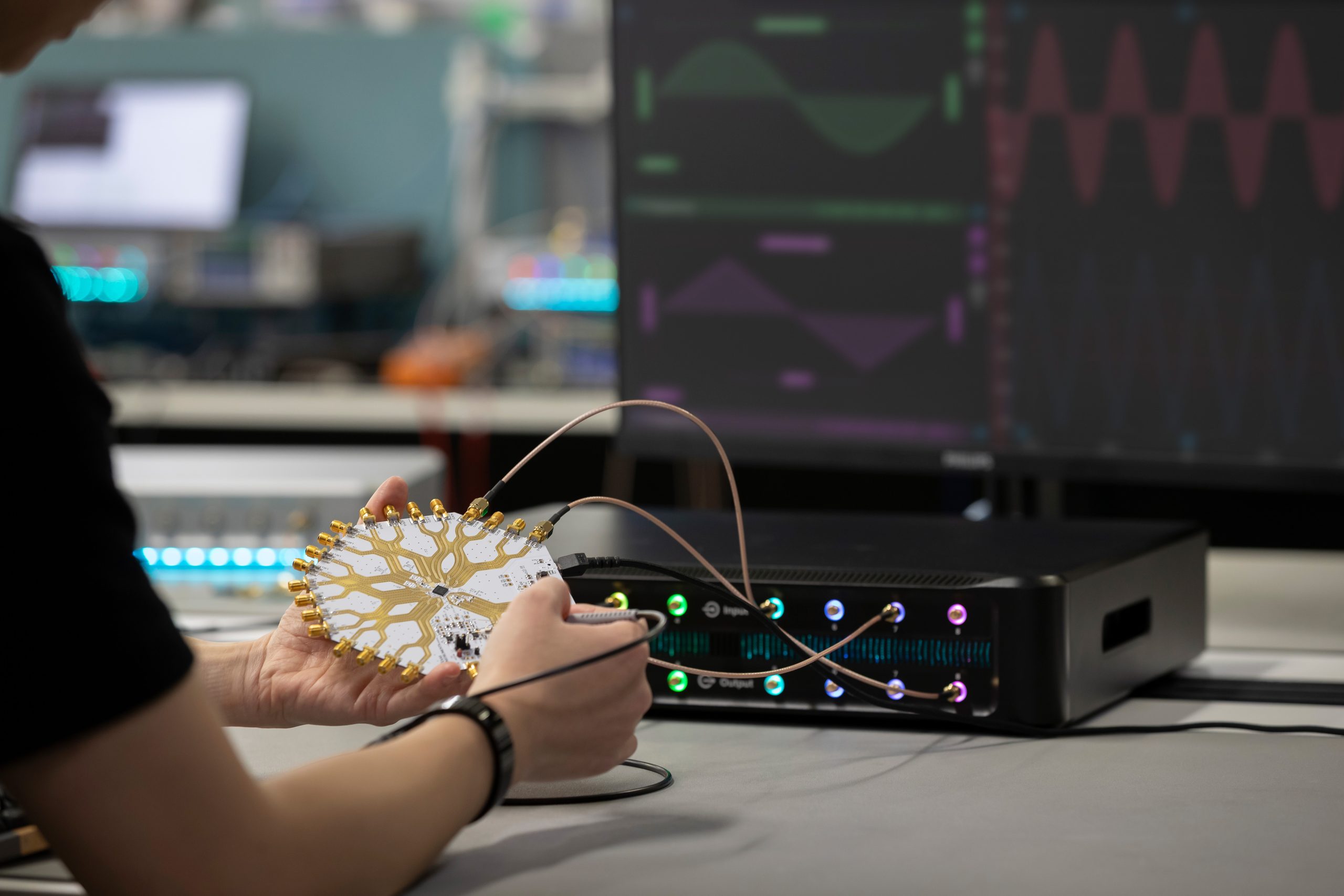

- Use ChatGPT to create custom VHDL code without needing any prior knowledge of digital logic design or programming.

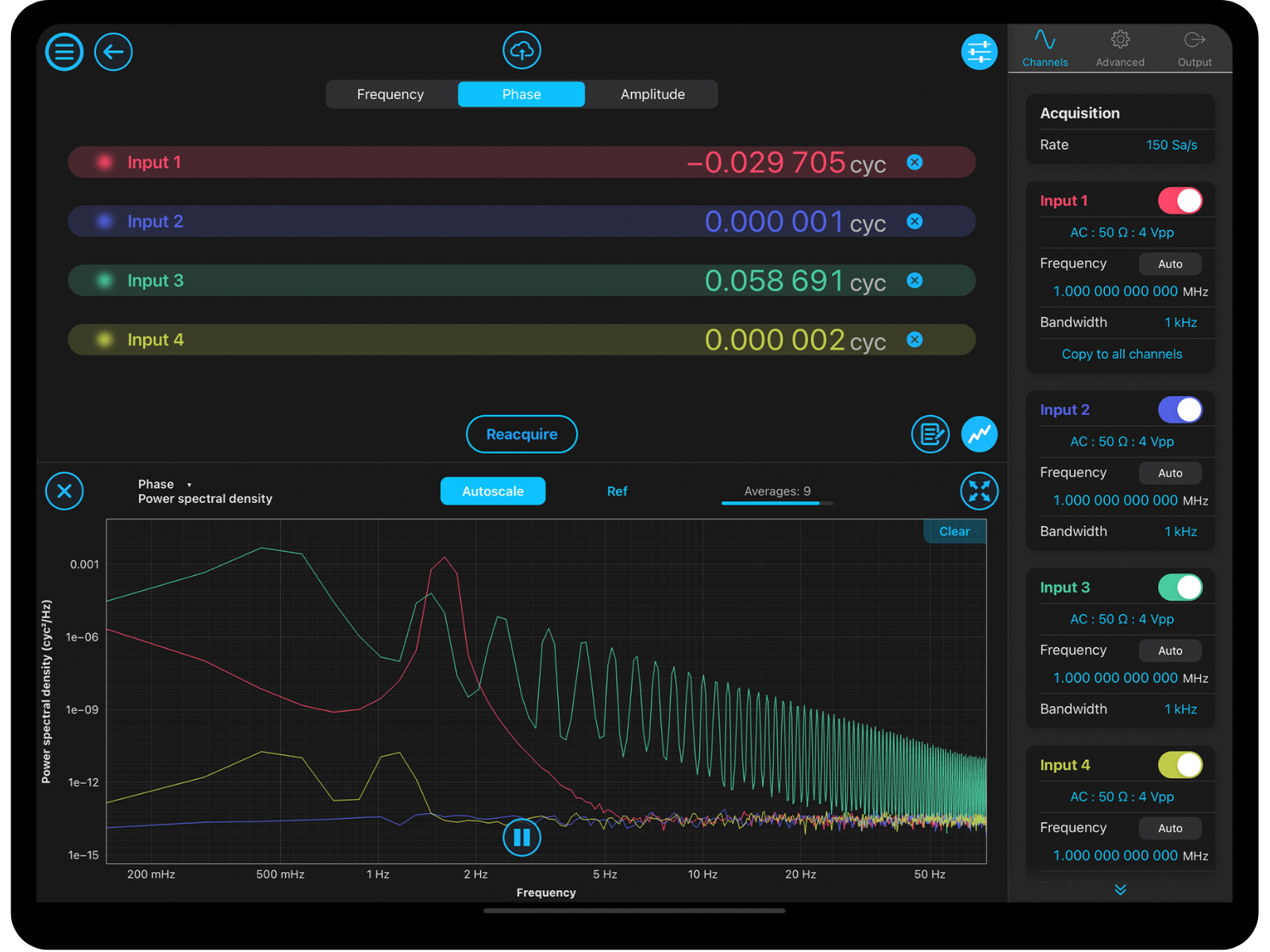

- Use Moku Cloud Compile to deploy the code directly to flexible, FPGA-based Moku hardware for instant use.

- Apply a range of examples, including full-wave rectifiers, debugging code, and data anomaly detection.

- Have important conversations with ChatGPT to develop improved outputs when the AI gets it wrong.

- Access our code repository and begin putting ChatGPT to work for your next project.

The webinar includes a presentation, demonstration, and live Q&A session.

Register for immediate access