Semiconductor device validation demands an increasingly wide range of measurements: gain-bandwidth, slew rate, harmonic distortion, phase noise, and more. As designs grow in complexity, test teams face mounting pressure to characterize more devices in less time without sacrificing measurement integrity.

Traditional approaches rely on racks of fixed-function instruments, each with its own driver stack, calibration cycle, and cabling. Scaling from one device under test (DUT) to many typically means multiplying that hardware, along with the cost, bench space, and maintenance burden that comes with it. Worse, even when more instruments are added, test execution often remains sequential, with each DUT waiting its turn for a shared resource.

This whitepaper introduces a different approach: combining Python-based test automation with FPGA-based instrumentation to achieve true parallel device testing. By offloading time-critical operations to reconfigurable hardware and using Python as a lightweight orchestration layer, engineering teams can dramatically reduce test time while improving repeatability and synchronization across channels.

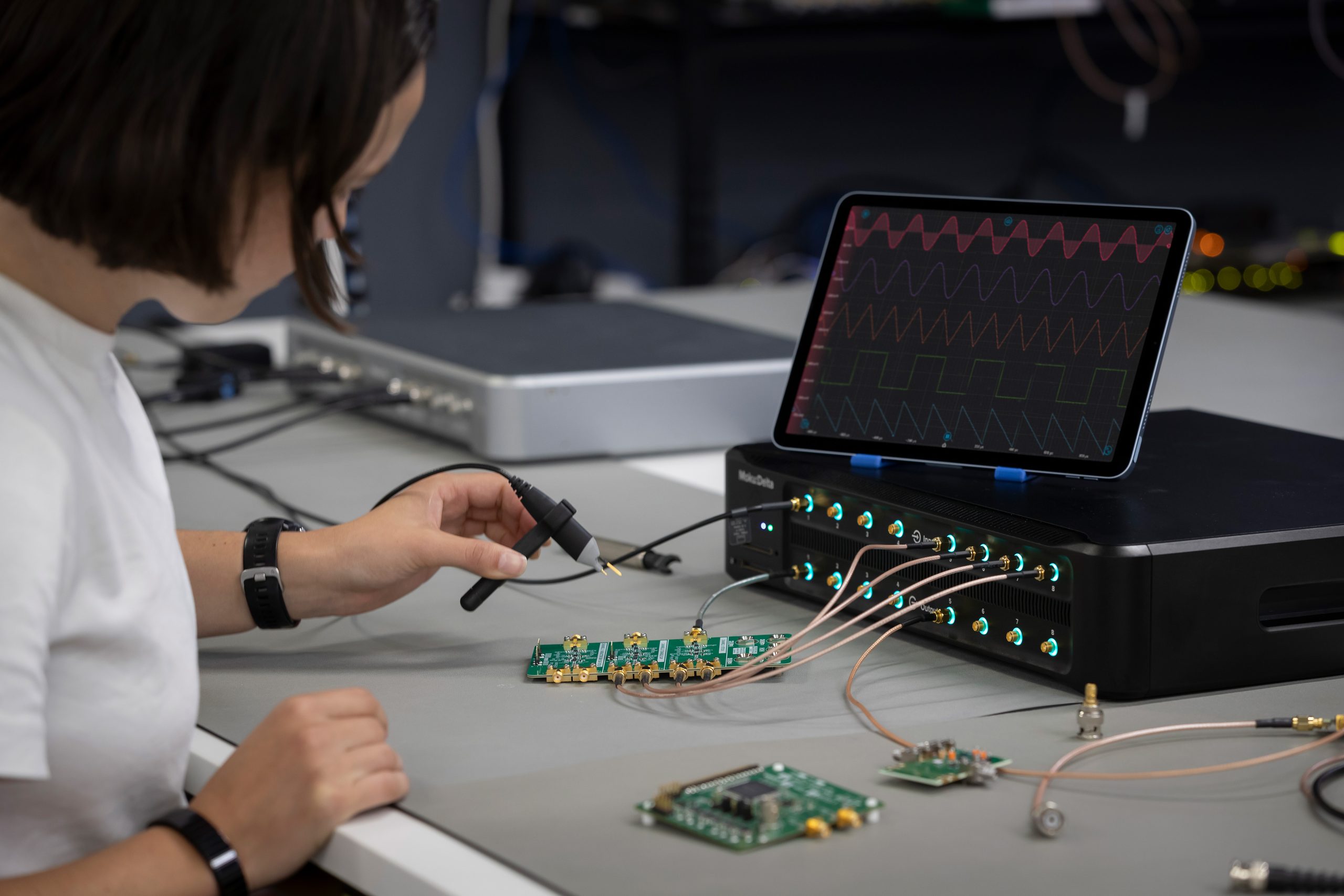

Figure 1: Multi-channel DUT test using Moku:Delta and the Frequency Response Analyzer

The Scaling Challenge

Single-device testing methods do not scale linearly. When validation teams attempt to increase throughput by adding more DUTs, they encounter compounding obstacles on both the hardware and software sides.

Hardware Bottlenecks

- Sequential reconfiguration: In a traditional setup, each instrument must be reconfigured for each DUT, adding significant overhead between measurements. This dead time accumulates quickly as the number of devices grows.

- Instrument contention: When multiple measurements share resources like signal generators or digitizers, they form queues. One measurement must complete before the next can access the hardware, reducing effective parallelism even when the test plan calls for concurrent operation.

- Cost and rigidity: PXI racks and benchtop instruments are expensive and difficult to reconfigure. Adding a new capability often means purchasing additional cards, re-cabling, and recalibrating rather than simply updating a configuration.

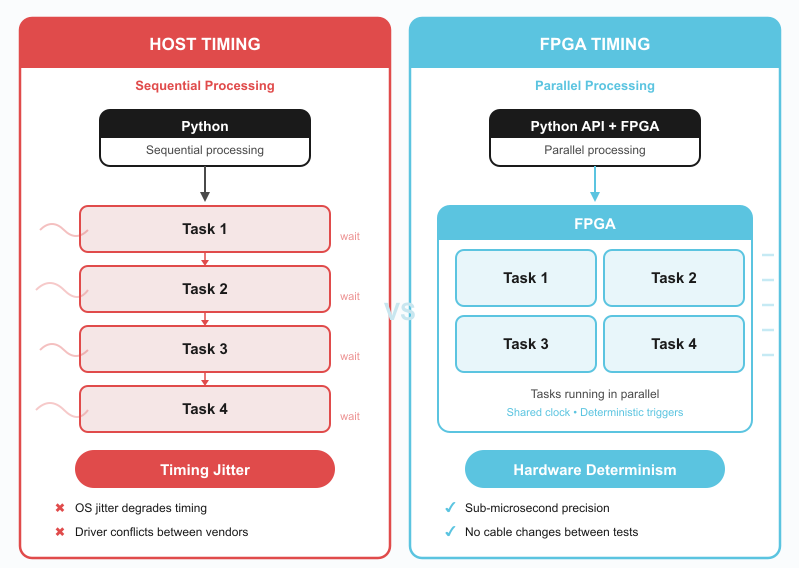

Software and Timing Issues - OS jitter: When a host CPU manages test timing, the operating system introduces non-deterministic delays. A background process or system update can steal milliseconds from a measurement, degrading synchronization between channels.

- Driver conflicts: Interfacing instruments from multiple vendors through a PXI chassis or VISA resource manager frequently causes driver and resource-locking conflicts, especially in complex setups.

- Timing drift: Without a shared clock reference and deterministic triggering, measurements across channels can drift apart, producing data that is difficult to compare and unreliable for pass/fail decisions.

Why FPGAs Are the Foundation for Parallel Test

FPGAs are already present inside many test instruments, typically handling timing distribution or basic triggering. The Moku platform from Liquid Instruments takes this much further, using the FPGA as the primary execution engine for measurements, signal generation, and real-time digital signal processing.

Figure 2: Scaling to multiple DUTs using a single hardware device, Moku:Delta

Deterministic Timing

FPGAs execute operations on strict hardware clock cycles, delivering sub-microsecond precision. Unlike CPU-based systems, where the operating system decides when tasks run, an FPGA processes every instruction at a predictable, fixed interval. This is essential for synchronized multi-channel acquisition where data sets must begin at the exact same sample.

True Hardware Parallelism

An FPGA can process multiple channels and control loops simultaneously by dedicating different sections of the chip to different tasks. There is no contention for shared resources because each operation has its own dedicated logic. The Moku platform takes advantage of this by running up to eight instruments concurrently on a single device, with 80 Gbps digital communication between instrument blocks for lossless real-time feedback loops.

Reconfigurability

Unlike fixed-function instruments, FPGAs can be reconfigured in seconds to perform entirely different operations. A section of the chip that was acting as an oscilloscope can become a spectrum analyzer or a frequency response analyzer with a single API call, no hardware changes required.

Scaling Architecture

Moku:Delta provides eight analog inputs, eight analog outputs, 32 digital I/O channels, and up to eight simultaneous instrument slots. Because instrument deployment is software-defined, scaling from two DUTs to eight requires only additional cabling and a parameter change in the Python script. There is no additional hardware to purchase, calibrate, or maintain.

Time Savings

Consider a validation sequence with four DUTs and three tests, each taking 10 minutes. A serial approach requires running each test on each device sequentially: 4 DUTs x 3 tests x 10 minutes, totaling two hours. With FPGA-based parallel execution, all four DUTs run simultaneously, reducing total test time to approximately 30 minutes, or even 10 minutes if all three tests can run concurrently using multiple instrument slots.

Figure 3: Sequential test processing with one or more test units vs. parallel DUT test using Python as the orchestration layer

Python + FPGA: The Software-Hardware Architecture

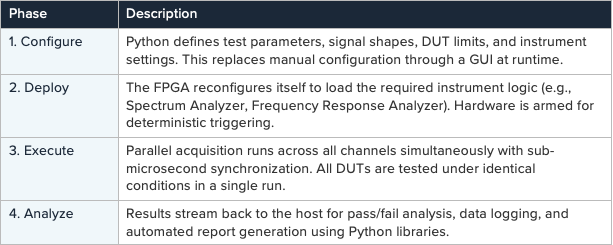

The parallel test architecture divides responsibilities cleanly between software and hardware, letting each do what it does best. The result is lower latency, higher throughput, and tighter control over every aspect of the measurement.

Python as the Orchestration Layer

Since the FPGA handles the signal generation, triggering, filtering, and real-time DSP, the host PC is left to manage high-level configuration, test sequencing, data aggregation, and reporting. The Moku Python API allows engineers to configure instruments, set parameters, and initiate measurements from a single, version-controlled codebase. Its rich ecosystem of data analysis tools (NumPy, SciPy, Matplotlib) makes it a natural choice for post-processing and visualization. MATLAB and LabVIEW APIs are also available for teams with existing workflows in those environments.

The Four-Phase Workflow

Case Study: Parallel Op-Amp Validation

To demonstrate these concepts in practice, consider validating semiconductor op-amp ICs, a common task for analog design and test teams. The objective is to characterize device performance across multiple specifications and generate validated datasheets.

Traditional Approach

A typical bench setup for even a few tests requires four to five separate instruments: an Arbitrary Waveform Generator for stimulus, an Oscilloscope and Spectrum Analyzer on the output, and a Frequency Response Analyzer for gain and phase measurements. Each instrument costs tens of thousands of dollars, has its own interface and driver, and requires dedicated cabling. Scaling to multiple DUTs means duplicating the entire setup or running tests sequentially.

FPGA-Based Parallel Approach

Using a single Moku:Delta, the same tests run concurrently across multiple DUTs with no physical cable changes between measurements. The Multi-Instrument Mode deploys up to eight software-defined instruments on the same FPGA, all sharing a common reference clock for time-coherent captures and reliable phase alignment.

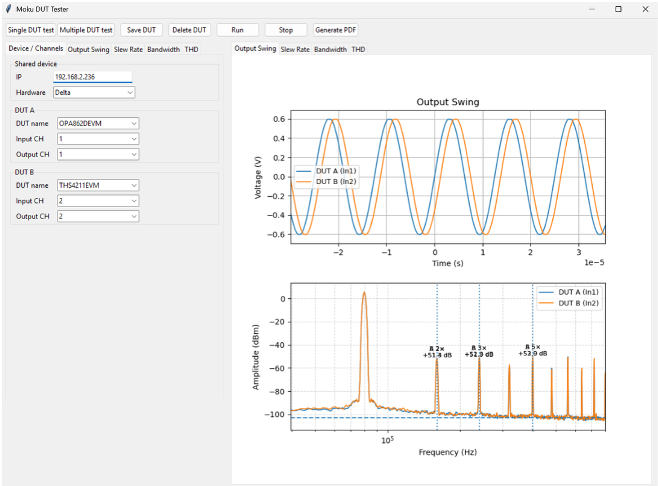

In a live demonstration, two op-amp evaluation boards (THS4211EVM and OPA862DEVM) were tested simultaneously across four key parameters:

- Output swing: A sine wave stimulus is generated by an embedded Waveform Generator within the Spectrum Analyzer. The frequency-domain response reveals clipping through harmonic content, while a simultaneous oscilloscope view shows the time-domain behavior, shown in Figure 4 and 5.

- Slew rate: A square wave input is applied, and the rising/falling edge slope is measured on the captured output.

- Closed-loop bandwidth: The frequency response analyzer sweeps a sine wave across the frequency range and measures the magnitude response. Python automatically identifies the −3 dB cutoff point.

- Total harmonic distortion: A fixed-frequency sine wave is applied, and the Spectrum Analyzer captures the harmonic content. Python computes THD from the measured spectrum.

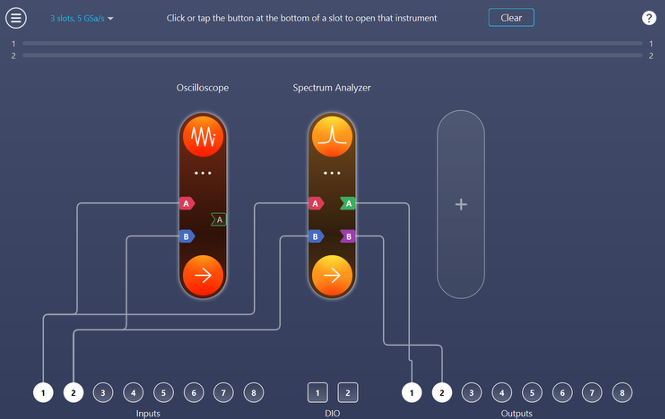

All instruments reconfigured programmatically between tests via Python API calls through a custom Python GUI (Figure 4). No technician intervention was required, and the entire test sequence for both DUTs completed in the time it would normally take to test a single device. The system also generated a PDF spec sheet summarizing all measurements with captured plots. Figure 5 illustrates the corresponding Moku app configuration for the output swing measurement shown in Figure 4.

Figure 4: Python GUI showing output swing results simultaneously measured from both DUTs (OPA862EVM and THS4211EVM)

Figure 5: Corresponding output swing test configuration from Figure 4 depicted in the Moku app

Conclusion

Full silicon device characterization requires a wide range of test equipment spanning time-domain, frequency-domain, and mixed-signal measurements. Integrating these instruments into a single, reconfigurable measurement platform addresses the core challenges of cost, rigidity, and throughput that test teams face when scaling from single-device validation to parallel production test.

By pairing Python as a flexible orchestration layer with the deterministic, truly parallel execution of FPGA-based hardware, engineering teams can achieve test times that were previously impractical, while maintaining the measurement integrity and synchronization that semiconductor validation demands.

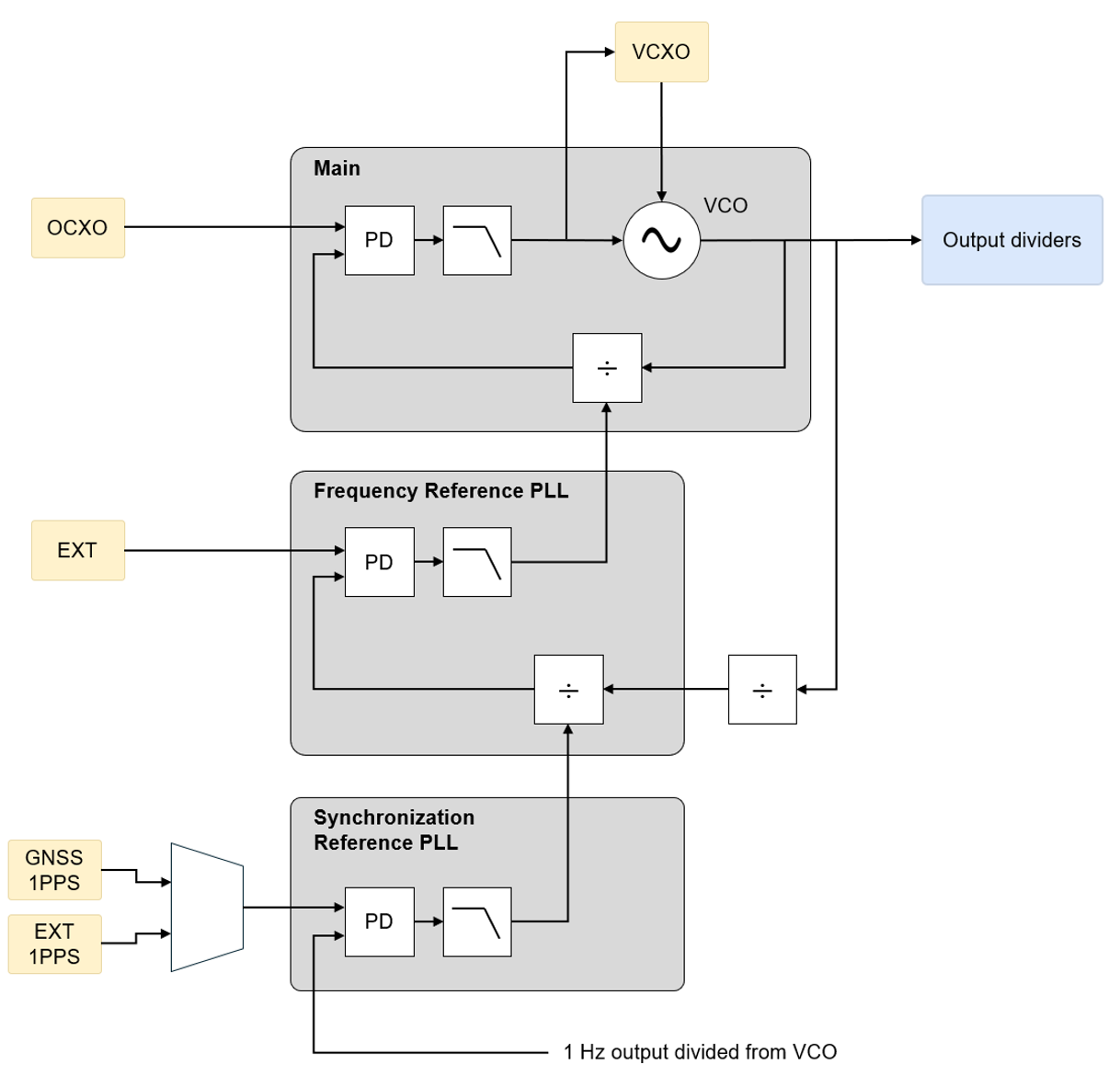

The Moku platform offers up to 2 GHz of real-time bandwidth, sub-10 nV/√Hz input noise, GPS-synchronized timing, and the ability to deploy up to eight instruments simultaneously on a single device, providing a powerful and adaptable foundation for the next generation of parallel test systems.

Learn More

Visit liquidinstruments.com to download the free Moku software, explore the semiconductor test resource center, or request a demo of parallel testing with Moku:Delta.